集微网报道(文/朱志磊)过去几十年,摩尔定律的演进推动了芯片制造工艺和设计架构的翻天覆地的变化。随着晶体管的尺寸接近物理极限,未来的先进设计和工艺将延续摩尔定律。(More Moore)、超过摩尔定律(More than Moore)和新器件(CMOS)等方向,EDA作为核心工具也需要进入新的发展时代,以支持更先进的工艺节点、更复杂的设计和制造和更多样化的设计应用。

另一方面,从2018年华为制裁导致国内半导体行业苏醒,到近期美国升级EDA出口禁令,国内EDA因人为筑起的“壁垒”,开辟了更广阔的市场空间。 . 随着国内芯片设计制造产业链的不断升级,华大九天、高伦电子、广利微等龙头企业相继上市,以及河建工软、新华章、信和、兴芯、新启源等数十家新势力. 随着崛起,国内EDA行业也进入了一个新的发展阶段。

从0到1的突破,全程还有35~40%的差距有待填补

中国的EDA产业起步不算晚。1990年代初,国内首个自主研发的EDA系统“熊猫”诞生。但由于芯片设计产业链缺乏土壤和国家对产业的扶持,中国EDA产业经历了近20年。多年寒冷的冬天。2018年之后,国内EDA将迎来创业浪潮。据集微咨询不完全统计,2021年EDA赛道上的融资事件将超过15个,融资公司超过12家,融资规模或超20亿元;从政策扶持到资金涌入,5次规模超13亿元的融资事件,推动了该领域的爆发式增长。

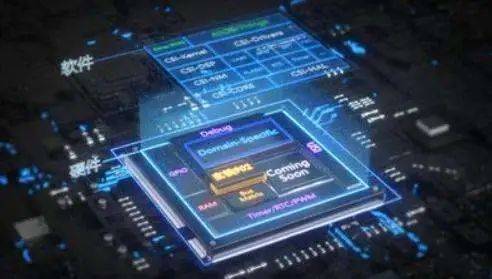

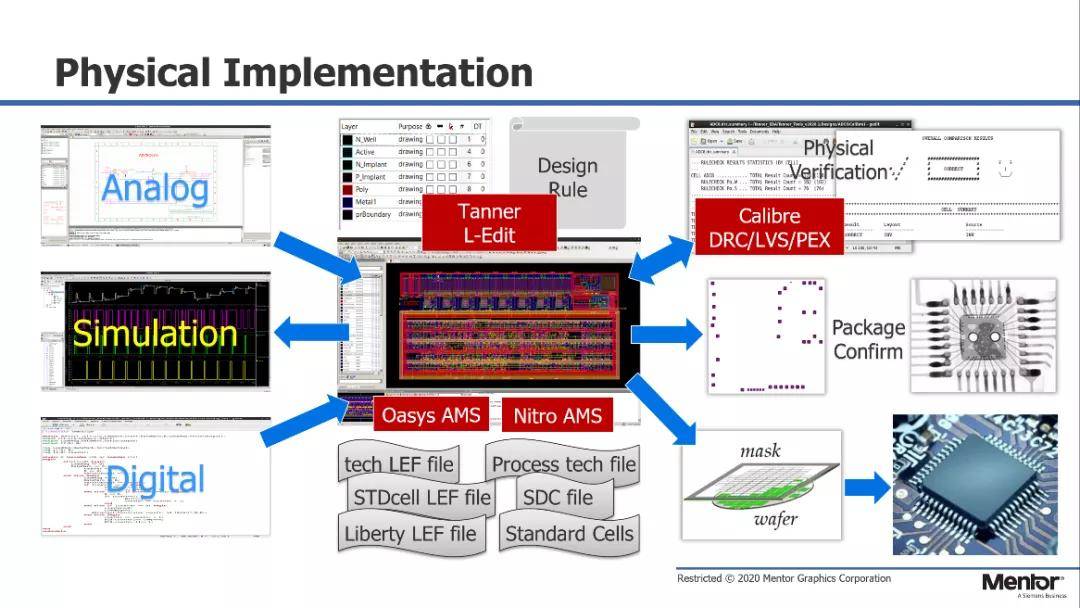

根据设计对象的不同,EDA工具可分为模拟设计、数字设计、晶圆制造、封装、系统五类。主流的点工具有数百种,包括芯片设计、晶圆制造、封装测试等。不同的工艺对EDA工具的功能要求不同,需要使用不同类型的点工具。经过几十年的发展,EDA行业的三大巨头,何(原创)已经实现了全流程的覆盖,在一些点工具上具有得天独厚的优势。如数字芯片设计、静态时序验证验证和SiP提供的优势;在模拟或混合信号定制电路和版图设计方面的优势;主要后端验证、可测试性设计和光学邻近校正。

纵观国内EDA的发展,我们仍然缺乏数字电路全流程和先进技术的支撑,因为EDA众多关键技术的每个子领域都存在极高的技术壁垒、人才壁垒和生态壁垒。但也有一些企业逐渐形成了全流程的突破和特定领域的一些点工具,并获得了一定的市场份额。例如,在上市公司中,华大九天实现了模拟电路全制程工具覆盖,在数字电路设计、平板显示电路设计、晶圆制造等领域也具有独特的技术优势;仿真验证EDA领域技术领先,近期发布了基于DTCO理念的承载EDA全流程创新的平台产品,进入了新的发展阶段;类 EDA 领域具有独特的价值。剩下的几十家新势力企业也都有自己的点工具产品。随着这些企业的快速成长,国内EDA在多个领域实现了从0到1的突破,进入了全流程建设的新阶段。

业内人士指出,目前国产EDA工具可以整体商业化、商业化,可以交付给行业,只能覆盖60%~65%的流程,也就是说还有35%约 40% 的点工具。仍有差距。例如,在 EDA 工具中占比最大的 RTL 仿真,其次是逻辑综合,目前还没有商用工具。一些工具已经开发出核心技术,可以试用,但在大规模推广中还有很多问题需要解决。技术的缺失不能满足行业的需求,所以做EDA的全流程是行业必须完成的首要任务。一方面存在差距,同时也缺乏先进的技术。现在国内有很多设计公司可以基于7nm甚至3nm进行设计,但是国内的EDA工具支持不了。一个很重要的原因是无法获得先进的技术。参数,它不能用它来调整和优化。

兴欣科技董事长兼总经理何青也表示,虽然近两年国内EDA行业发展如火如荼,但真正能够实现商业化应用的数字EDA工具还比较少。“兴欣创始团队2018年回国,从0开始,用了四年时间,实现了EDA工具的商业化。” 何庆解释说,数字芯片从设计到流片成本高,需要的EDA工具种类多,要求高。要实现数字化EDA全流程,单靠一家企业是行不通的。

和建工业软件认为,目前数字芯片的规模往往是百亿门,而随着技术的进步,流片成本居高不下,流片失败的损失无法估量,验证调试是关键。越来越多的解锁流片。成败的关键环节成为研发工具成本占比最高的环节。因此,验证领域的突破对于中国芯片产业的发展至关重要。验证调试工具的架构和技术需要随着验证流程和方法论的发展而不断创新,国外厂商由于长期积累难免有包袱。在当前时间节点,

要实现国产EDA验证工具的突破,最重要的是全面提升规模、性能和自动化程度。因此,公司也选择了验证作为EDA工具的第一个突破点。只有解决验证中的复杂问题,才能帮助国内芯片企业设计出具有国际竞争力的产品。河建工业软件去年推出了FPGA原型验证系统,今年6月又发布了UV APS的新功能升级版。首次真正实现系统级Sign-off功能,可导入多种格式的IC、、、PCB数据,支持全面的系统互连一致性检查(-Level LVS),大幅提升检测效率,图形化显示、灵活性和准确性。

芯启源EDA&IP销售总经理邱业敏指出,随着先进制造工艺的不断迭代,芯片设计成本呈指数级飙升。不仅芯片的验证设计复杂,软件也变得异常复杂。软件团队需要更多的验证工具来并行开发,以确保芯片的成功和上市时间。然而,目前验证仿真环节的痛点是软硬件验证脱节。软件开发使用传统的原型验证平台,而硬件开发使用专用的硬件仿真器。前者功能少,诊断调试能力有限。后者是昂贵的和系统级的。或者软件的验证效率很低。随着工艺的发展,芯片设计也对验证工具提出了新的要求,包括提高IC研发效率、最大限度地利用流片资源、保证流片成功率等。

邱业敏透露,公司其实已经低调研发了一款数字RTL仿真工具,去年就已经提供给客户,近期也有部分成功录音,证明可以解决很多用户痛点。客户甚至充当“备胎”。也有一些客户不断提出更多的要求。比如不同行业的RTL需要不同的时钟,复杂度、子卡、接口也不同。通用的功能比较少,工具需要不断的优化和适配。但在客户提出要求的过程中,也帮助鑫启源对工具进行了迭代和打磨,这对于RTL仿真工具尤为重要。

“仿真真的很难,即使产品商业化,也要两三年的时间。所以国内的EDA仿真不多,重点是验证。我们也希望有更多的合作伙伴朋友加入。” 邱业敏说,“前期我们通过牺牲一些功能来实现性能,后期需要不断完善功能和语言集的丰富性,调试能力还要进一步提升。”

EDA云化成趋势,安全是最大障碍

从2010年和2011年开始,EDA、EDA等国际EDA巨头纷纷提出EDA云迁移的概念。之后,英特尔、英伟达等芯片巨头开始探索EDA云工具的应用。2015年后,公有云架构逐渐稳定,数据安全体系逐渐成熟。如今,EDA云平台的工具和运行环境已经逐步整合,产品可以大规模复制到不同行业并提供给客户。可以说,EDA云平台产业已经到了商业发展的关键节点。

对于芯片设计公司/部门来说,如何在快速实现产品开发、提高效率、降低成本的同时,可扩展性巨大的“云”成为了很好的依靠。然而,如何安全可控地将更多设计流程上云,利用云计算弹性扩展,更好地对接低端工厂,实现更快的产品上线,还有很多挑战需要解决。

集微咨询研究指出,到2024年,60%的前沿芯片设计将在云端完成,而2019年这一比例不到5%。芯片设计公司采用设计上云的三大驱动因素包括:

1.随着高级节点工艺设计变得越来越复杂,这些设计所需的计算能力也急剧增加。尖端的芯片设计周期需要很高的算力成本,需要大量的硬件基础设施投资;

2.计算能力需求的弹性是 IC 设计人员面临的与基础设施相关的最大挑战之一。在芯片设计周期的不同阶段,工程师需要不同的计算资源。物理验证、电路仿真和静态时序分析需要高计算能力配置。诸如此类的计算能力要求的波动使得固定和有限的计算能力资源可能成为设计周期中的瓶颈;

3.随着自动驾驶、汽车电动化、人工智能和5G等应用的兴起,越来越多的初创公司开始投资芯片设计,但这些小公司大多缺乏足够的资金灵活性,或者缺乏投资能力芯片设计所需的计算资源(本地基础设施)。

副总裁熊文表示,半导体行业是云迁移的最后堡垒,很多行业已经意识到这一点。然而,半导体公司普遍认为数据安全与生命一样重要。对云来说,还是有一些顾虑的。但现在芯片企业的成本负担越来越重,包括人力、IP授权、制造流片,尤其是芯片设计后期EDA仿真所需的大量机房资源。与传统EDA工具相比,云EDA用户无需为不必要的功能付费,降低了IT硬件投资和工具维护的人工成本。在运营成本不断攀升的背景下,EDA上云将是必然趋势。芯片设计公司不断吸收变化以优化他们的设计。对此,虽然不是全部上云,但至少EDA的部分功能会慢慢上云。云EDA的采用可以改变企业的ROI(投资回报率)。对中小型初创公司非常有吸引力。

随着越来越多的初创芯片设计公司进入自动驾驶、人工智能、5G等领域,HPC、领先的代工厂和EDA公司推动芯片设计上云的最新趋势代表着芯片设计创新的新时代.,使用云计算可以帮助他们解决设计工具和硬件基础设施的高成本。虽然EDA迁移到云端无疑已经成为一种趋势,但进展非常缓慢。集微咨询认为,传统设计方式的转变导致客户使用习惯的改变,EDA项目成本逐渐从资本支出Capex转变为运营支出Opex,产品快速上线的压力也需要灵活的算力分配。此外,

熊文总结了EDA硬件在上云之路上面临的四大壁垒,包括技术壁垒、数据安全壁垒、商业模式壁垒和成本壁垒。对于用户特别关心的安全问题,他详细阐述了的考虑。一方面,为了企业通过外网访问内网时的数据安全,主要采用Palo Alto防火墙技术,外网访问采用白名单方式,用户可以使用VPN或私网访问. 另一方面,访问内网后的数据安全。 在客户数据接入内网后提供了一套物理隔离和保护措施。同时,

国内EDA进入新的发展阶段,从技术积累到格局重构

虽然目前国产EDA仍无法像海外巨头一样提供全流程覆盖解决方案,但其在一些关键环节的突破和技术积累也让国产EDA工具在高度集中的市场中逐渐分得一杯羹。我们现在面临的问题是,如何在下一阶段的全过程发展中实现从技术积累到格局重构的突破?

1.星火燎原,燎原燎原,努力打造EDA全流程

在何清看来,国内半导体行业并没有完美的弯道超车方式,只能用勤奋来提速,换取发展时间。何清指出,数字化工具链的全流程,不可能一家公司实现。对于一个企业来说,它所能做的就是在点工具上有所突破,整合不同“点优势”的产品和技术。20年左右可以建成一套国产数字EDA全流程工具。

EDA工具链很长,需要全行业的共同努力才能实现全流程的目标。业内普遍认为,一个EDA产品从开发到商业上线需要5年时间。当前形势下,本土企业正在努力抓紧时间,有望加快这一进程。要实现全系统支持,除了数字和模拟开发工具外,还需要补充制造、封装和应用端工具。乐观估计,最早要到2027年才能实现。

这个过程可能需要至少3000名研发人员的投入,而且要有足够的高层次人才;产业每年需投资4-50亿元,未来5年累计超过200亿元;也需要解决目前国内的EDA厂商。对于战争,重复投资和浪费。

2.打破“差距”和“偏见”,让客户更愿意使用国产工具

全球EDA巨头花费数十年的研发和并购,积累了今天的优势和深厚的生态壁垒。国内半导体企业长期使用国际巨头的产品,形成了强大的用户粘性。对产品技术开发水平的固有认知,小公司不愿试错,大公司的门槛很高。更重要的是,EDA工具的选择关系到流片的成功率。客户更换 EDA 工具带来的风险极高。当客户使用国产EDA跑出与国际巨头EDA工具不一致的数据时,国内厂商甚至需要说明结果。.

河建工业软件认为,EDA软件非常复杂,技术壁垒很高。最重要的是不仅要开发工具,还要不断迭代。只有生态和客户的支持,才能形成闭环。因此,我们必须以开放的心态拥抱当地客户的实际需求,实现差异化优势。产品面世后可进一步加强合作,不断打磨产品,不断突破现有工具的技术包袱和技术壁垒,进一步提升验证调试效率,实现易用性和耐用性,实现双赢。通过与IC厂商的相互促进、相互促进,

邱业敏表示,公司这几年做的工具,并没有特别好的抛光应用场景。很多客户因为自身的压力,没有给国内的EDA公司太多机会,要尽快流片和量产,但这种情况现在正在改变。邱业民希望政府能给予更多的政策引导,对国产EDA工具的购买和使用给予补贴。随着美国制裁的收紧,国内EDA的窗口已经不多了。如果客户能给予更多打磨的机会,国产EDA就能更快成熟,未来也能更好地回馈行业。.

华大九天董事长刘卫平提出了几点意见。首先,他应该从战略的角度引导下游客户加大产业链的战略合作,而不仅仅是单纯的市场和利益。其次,仅靠少数几家大公司带动行业动力有限,仍需市场化。这就需要国产EDA工具经得起市场的考验,前期依靠国家战略引导客户,后期通过自身产品的竞争力赢得市场。最后,从政策层面鼓励或引导本地化应用,比如设立本地化奖励基金,鼓励客户使用本地化产品。

3.并购整合,格局重构

回顾EDA行业的诞生和发展国产楼宇自控,也是一部EDA巨头并购的历史。与领先的EDA公司在发展过程中进行大量并购不同,国内EDA行业仍处于发展初期。只有华大九天在2010年收购了华天中汇,格伦电子分别在2019、2021收购。在少数案例中,比如博大威等,河间实业近期的一项并购计划被英国否决。随着国内EDA行业初创企业的出现和发展,行业龙头企业也有望通过并购快速拓展产品线,提升核心竞争力。

刘卫平表示,国内数字化全流程的实现无非是几个手段:一是融合。在经营情况复杂的情况下,寻找合适的合作伙伴进行并购整合;第二,投资。如果无法整合,寻找合适的合作伙伴和投资机会;三是联合运营,技术开发和业务运营合作,以“你有我,我有你”的方式串联各种工具。

何庆补充说,这个融合与合作的过程需要解决两个层面的问题。首先是技术层面,需要在底层数据格式上进行统一,实现设计数据的无缝传输。二是文化层面。不同团队的整合需要解决文化和理念上的差异。

写在最后

回顾全球集成电路设计发展,展望未来,设计领域呈现出以下三个新的发展趋势:设计异构、芯片与算法系统集成、敏捷设计。行业的变化使EDA工具发生了深刻的变化。

美国的禁令也是一把双刃剑,迫使新一代中国半导体企业迅速脱颖而出。

国内EDA产业逐渐壮大,星火燎原成为大草原。他们能否在行业和国内浪潮的双重变革下重塑EDA产业格局?我们可能还需要放眼长远,给EDA本地化更多的信心和时间。(校对/张益群)